KEGIATAN BELAJAR 5: REGISTER

a. Uraian Materi

Register adalah sekelompok flip-flop yang dapat dipakai untuk menyimpan dan untuk mengolah informasi dalam bentuk linier.

Ada 2 jenis utama Register yaitu:

1. Storage Register (register penyimpan)

2. Shift Register (register geser)

Register penyimpan (Storage Register) digunakan apabila kita hendak menyimpan informasi untuk sementara, sebelum informasi itu dibawa ke tempat lain. Banyaknya kata/bit yang dapat disimpan, tergantung dari banyaknya flip-flop dalam register.

Satu flip-flop dapat menyimpan satu bit. Bila kita hendak menyimpan informasi 4 bit maka kita butuhkan 4 flip-flop.

Contoh: Register yang mengingat bilangan duaan (biner): 1101 terbaca pada keluaran Q.

Shift Register adalah suatu register dimana informasi dapat bergeser (digeserkan). Dalam register geser flip-flop saling dikoneksi, sehingga isinya dapat digeserkan dari satu flip-flop ke flip-flop yang lain, kekiri atau kekanan atas perintah denyut lonceng (Clock).

Dalam alat ukur digit, register dipakai untuk mengingat data yang sedang ditampilkan.

Ada 4 Shift Register yaitu:

1. SISO (Serial Input Serial Output)

Gambar Register SISO yang menggunakan JK FF

Prinsip kerja:

Informasi/data dimasukan melalui word in dan akan dikeluarkan jika ada denyut lonceng berlalu dari 1 ke 0. Karena jalan keluarnya flip-flop satu dihubungkan kepada jalan masuk flip-flop berikutnya, maka informasi didalam register akan digrser ke kanan selama tebing dari denyut lonceng (Clock).

Tabel Kebenaran (Misal masuknya 1101)

| Clock ke | Word in | Q1 | Q2 | Q3 | Q4 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 |

| 3 | 1 | 1 | 0 | 1 | 0 |

| 4 | 1 | 1 | 1 | 0 | 1 |

Register geser SISO ada dua macam yaitu:

a) Shift Right Register (SRR)/Register geser kanan

b) Shift Left Register (SLR)/Register geser kiri

c) Shift Control Register dapat berfungsi sebagai SSR maupun SLR

Rangkaian Shift control adalah sebagi berikut:

Rangkaian ini untuk mengaktifkan geser kanan/kiri yang ditentukan oleh SC. Jika SC=1, maka akan mengaktifkan SLR. Jika SC=0, maka akan mengaktifkan SRR. Gambar rangkaian selengkapnya adalah sebagai berikut:

Keterangan:

Jika SC=0,maka input geser kanan akan aktif. Keluaran NAND diumpamakan ke input DFF1 dan setelah denyut lonceng berlaku (saat tebing depan), maka informasi diteruskan ke output Q1. Dan output Q1 terhubung langsung keoutput DFF2 berikutnya sehingga dengan proses ini terjadi pergeseran ke kanan.

TABEL KEBENARAN (jika input 1101)

| Clock ke | Input | Q1 | Q2 | Q3 | Q4 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 |

| 4 | 1 | 1 | 0 | 1 | 1 |

Informasi digit digeser kekanan setiap ada perubahan pulsa clock tebing atas. Geser kanan berfungsi sebagai operasi aritmatika yaitu pembagi dua untuk tiap-tiap flip-flop.

Jika SC = 1 , maka akan mengaktifkan input geser kiri. Output NAND masuk ke input D-FF4 dan setelah diberi pulsa clock informasi dikeluarkan melalui Q4 dan keluaran Q4 dihubungkan ke input D-FF3, keluaran D-FF3 dimasukan ke D-FF berikutnya, sehingga dengan demikian terjadi pergeseran informasi bit ke arah kiri.

TABEL KEBENARAN (jika input 1101)

| Clock ke | Input | Q1 | Q2 | Q3 | Q4 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

| 2 | 1 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 0 |

| 4 | 1 | 1 | 1 | 0 | 1 |

Register geser kiri berfungsi sebagai operasi aritmatika yaitu sebagai pengali dua untuk tiap-tiap flip-flop.

2. Register Geser SIPO

Adalah register geser dengan masukan data secara serial dan keluaran data secara parelel.

Gambar rangkaiannya adalah sebagai berikut: (SIPO menggunakan D-FF)

Cara kerja:

Masukan-masukan data secara deret akan dikeluarkan oleh D-FF setelah masukan denyut lonceng dari 0 ke 1. Keluaran data/informasi serial akan dapat dibaca secara paralel setelah diberikan satu komando (Read Out). Bila dijalan masuk Read Out diberi logik 0, maka semua keluaran AND adalah 0 dan bila Read Out diberi logik 1, maka pintu-pintu AND menghubung langsungkan sinyal-sinyal yang ada di Q masing-masing flip-flop.

Contoh: Bila masukan data 1101

TABEL KEBENARANNYA:

| Read Out | Clock | Input | Q1 Q2 Q3 Q4 | A B C D |

| 0 | 0 | 0 | 0 0 0 0 | 0 0 0 0 |

| 0 | 1 | 1 | 1 0 0 0 | 0 0 0 0 |

| 0 | 2 | 1 | 1 1 0 0 | 0 0 0 0 |

| 0 | 3 | 0 | 0 1 1 0 | 0 0 0 0 |

| 0 | 4 | 1 | 1 0 1 1 | 0 0 0 0 |

| 1 | | | 1 0 1 1 | 1 0 1 1 |

3. Register Geser PIPO

Adalah register geser dengan masukan data secara jajar/paralel dan keluaran jajar/paralel.

Gambara rangkaiannya adalah sebagai berikut: (PIPO menggunakan D-FF)

Cara kerja:

Sebelum dimasuki data rangkaian direset dulu agar keluaran Q semuanya 0. Setelah itu data dimasukkan secara paralel pada input D-FF dan data akan diloloskan keluar secara paralel setelah flip-flop mendapat pulsa clock dari 0 ke 1.

Contoh:

TABEL KEBENARAN:

| Clock | D1 D2 D3 D4 | QD QC QB QA |

| 0 | 1 1 0 1 | 0 0 0 0 |

| 1 | 1 1 0 1 | 1 1 0 1 |

| 2 | 1 0 0 1 | 1 0 0 1 |

| 3 | 0 0 0 1 | 0 0 0 1 |

4. Register geser PISO

Adalah register geser dengan masukan data secara paralel dan dikeluarkan secara deret/serial.

Gambar rangkaian register PISO menggunakan D-FF adalah sebagai berikut:

Rangkaian diatas merupakan register geser dengan panjang kata 4 bit. Semua jalan masuk clock dihubungkan jajar. Data-data yang ada di A, B, C, D dimasukkan ke flip-flop secara serempak, apabila dijalan masuk Data Load diberi logik 1.

Cara Kerja:

§ Mula-mula jalan masuk Data Load = 0, maka semua pintu NAND mengeluarkan 1, sehingga jalan masuk set dan rerset semuanya 1 berarti bahwa jalan masuk set dan reset tidak berpengaruh.

§ Jika Data Load = 1, maka semua input paralel akan dilewatkan oleh NAND. Misal jalan masuk A=1, maka pintu NAND 1 mengeluarkan 0 adapun pintu NAND 2 mengeluarkan 1. Dengan demikian flip-flop diset sehingga menjadi Q=1. Karena flip-flop yang lainpun dihubungkan dengan cara yang sama, maka mereka juga mengoper informasi pada saat Data Load diberi logik 1. Setelah informasi berada didalam register, Data Load diberi logik 0. Informasi akan dapat dikeluarkan dari register dengan cara memasukkan denyut lonceng, denyut-demi denyut keluar deret/seri. Untuk keperluan ini jalan masuk D dihubungkan kepada keluaran Q.

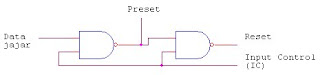

Ada juga register yang dapat digunakan sebagai Shift register SISO maupun PIPO dengan bantuan suatu control sbb:

Input Control = 0, berfungsi sebagai register geser SISO

Input Control = 1, berfungsi sebagai register geser PIPO

| Data | IC | Preset | Reset |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 |

Rangkaian kontrol diatas dapat disimbolkan sbb:

Rangkaian selengkapnya adalah sbb:

Catatan:

Jika IC=0, maka input yang dimasukan ke D0, D1, D2, D3 tidak mempengaruhi keadaan output QA, QB, QC, QD tetapi yang mempengaruhinya adalah data yang dimasukkan ke input D-FF secara serial, maka pada kondisi ini rangkaian akan bekerja senagai register geser SISO.

Jika IC=1, maka input yang dimasukkan ke gate D seri tidak akan mempengaruhi output, tetapi output dipengaruhi oleh data paralel (D0, D1, D2, D3).

Input dimasukkan secara serempak dan keluaran ditunjukkan secara serempak begitu pulsa clock berguling dari 1 ke 0, maka pada kondisi ini rangkaian akan bekerja sebagai registeer geser PIPO.

5 komentar:

mantap materinya gan ..

lebih komplit lagi gan materinya

mantap bro

gan kalo register PISO dengan JKFF gimana ya rangkaiannya?

semoga penulisnya belum bosen

mantap materinya gan ..

lebih komplit lagi gan materinya

mantap bro

gan kalo register PISO dengan JKFF gimana ya rangkaiannya?

semoga penulisnya belum bosen

Posting Komentar